What is the value of r0 after executing the following instruction sequence?

MOV r0, #200

MOV r5, #1

STR r3, [r0, r5, LSL#3]!

When linking with the standard C library, which library functions MUST be redefined in order to port your code to a new piece of production hardware?

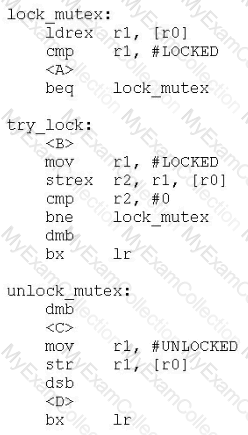

The following pair of functions implement a simple mutex spinlock which might be used to protect a critical code section in a multi-threaded application. The address of the lock variable is in r0.

In order to minimize power while waiting for the lock to be available. SEV and WFE instructions can be used to place the processor in a low power state while waiting for the lock to become available. At which points should these instructions be placed?

Which of these items is typically shared between threads running in the same Operating System (OS) process?

Which of the following properties is a required characteristic of a Symmetric Multiprocessing (SMP) system?

When a linker is removing unused sections during a static link (for example, -remove or -gc-sections), it finds the sections to keep by following all relocations starting from:

Which power mode describes the state where the ARM processor is powered down, but its Level 1 caches remain powered?

For Cortex-A series cores, what instruction(s) are recommended to implement a mutex or semaphore?

In which of these cases would code have better performance when compiled for Thumb state than when compiled for ARM state?

How many bytes of stack are needed to pass parameters when calling the following function?

int foo( short arg_a, long long arg_b, char arg_c, int arg_d )

Within the ARMv7 architecture, which one of the following features is unique to the ARMv7-A profile?

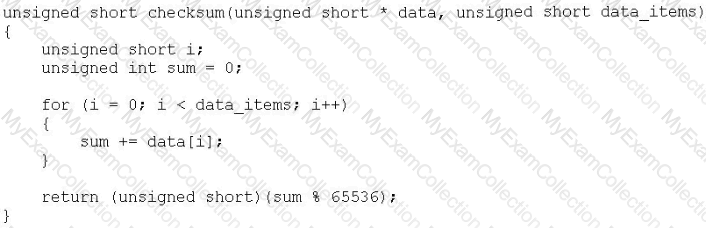

In an ARMv7-A system, the following C function calculates a simple checksum for an input data packet of variable length. The checksum is defined to be the sum of all of the 16-bit data items in the packet modulo 65536. The parameter data_items contains the number of 2-byte data items in the packet, and it cannot be zero by design.

When using an ARM compiler, which TWO of the following optimizations could improve the performance of this code? (Choose two)

Which of these processors is only available as a single core configuration?

On an ARM processor that does not implement Security Extensions, which one of the following can be the starting address of the exception vector table?

To ensure optimum efficiency when programming in C, what is the recommended maximum number of arguments to be passed to a function?

In a symmetric multi-processing (SMP) software architecture, which of the following pairs of statements are TRUE? (Select the option in which BOTH statements are TRUE).

What are the values of the NZCV bits in the CPSR after executing the following instructions?

LDR R0, = 0xFFFFFFFF

ADDS R0, R0, #1

In a Cortex-A9 MPCore cluster with four processors, which of the processors can be interrupted by a software-generated interrupt?

When developing a product using the standard ARM C library, what is the minimum effort required to re-target all platform-specific functions in the library?

In an experiment, the time taken for an application to complete a given task is measured using a stopwatch. Which THREE of the following make up the total time? (Choose three)

Which of the following is an advantage of the single-step debug technique?

According to the AAPCS, which of the following statements is TRUE with regard to preservation of register values by a function?

In an ARMv7-R processor, with which level of the memory system is the Memory Protection Unit (MPU) associated?

A 32KB 4-way set associative instruction cache supports a cache line size of 64 bytes. How many bits are required to index a cache line in a way?

An external debugger would need to clean the contents of the processor data cache in which of the following cases?